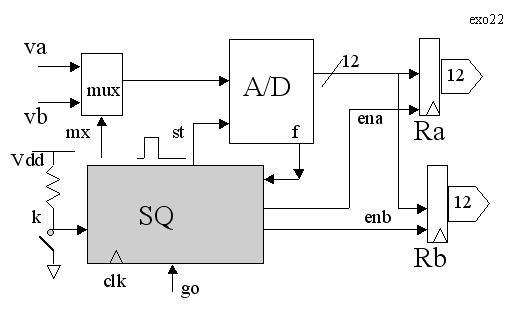

Le circuit ci-dessous a pour fonction, la conversion analogique/numérique en continue sur deux voies des signaux Va et Vb.

Les valeurs numériques, codées sur douze bits, sont chaque fois rangées dans les registres de sortie respectifs Ra et Rb.

Bien sur, les niveaux en entrée Va sont destinés au registre Ra et ceux de Vb au registre Rb. Enfin, nous disposons de

l'option conversion sur une seule voie (Va) par la fermeture du contacteur K.

Détail:

- Mux est un multiplexeur analogique (switch) à deux positions controlé par la broche de controle mx.

mx=0, Va est connecté.

mx=1, Vb est connecté.

- Le bloc A/D est un convertisseur analogique/numérique sur douze bits. Sur commande d'une impulsion appliquée sur l'entrée de controle St (start), la procédure de conversion démarre tandis que dans le mème temps la sortie f (fin de conversion) descend à 0. f ne remonte au niveau logique 1 qu'une fois la conversion terminée. La donnée numérique doit alors ètre mémorisée dans un des registres de sortie selon la valeur logique du commutateur K.

interne au convertisseur en attendant la prochaine demande de conversion.

- Ra et Rb sont deux registres de douze bits. Tout résultat de conversion de Va se retrouvera dans Ra. Tout résultat de conversion de Vb se retrouvera dans Rb.

- Ce circuit travaille en continu, selon deux modes sélectionnés par le commutateur K.

Si K='0' (K fermé): Il y a conversion continue de Va uniquement, avec résultat dans Ra.

Si K='1' (K ouvert): Il y a conversion continue mais en alternance de Va et Vb.

Pour K = '1', la fréquence d'échantillonnage des signaux analogiques Va et Vb est évidemment deux fois plus faible que la fréquence d'échantillonnage de Va uniquement pour K = '0'.

- ena et enb sont les broches de controle de demande de chargement des registres.

- Le séquenceur SQ dispose d'une entrée de remise à zéro directe Rd active à l'état bas.

Toute commande (mx, st, ena, enb) devra ètre exempte de tout risque d'aléa.

Travail demandé:

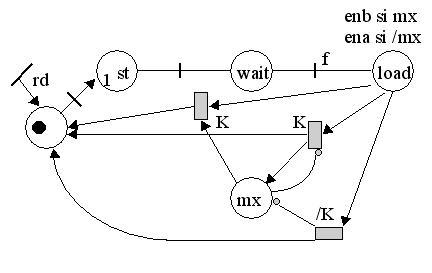

Modélisation du séquencement.

Synthèse et matérialisation (L'ensemble du design est "totalement synchrone" à l'exception de l'intervention du reset direct Rd).